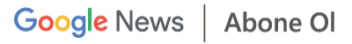

Yeni nesil çipler için arka taraf güç dağıtım ağı (BSPDN), gelecekteki proses teknolojisinin iyi bilinen ve yaygın olarak tartışılan bir avantajı. Intel ve TSMC bir süredir BSPDN hakkında konuşurken, Samsung yakın zamanda arka taraf güç dağıtımı deneyleri hakkındaki ayrıntıları paylaştı. Görünüşe göre şirket bu yenilikten ciddi kazanımlar elde etmeyi hedefliyor.

Samsung Electronics, Haziran ayı sonlarında VLSI Sempozyumu’nda sunulan bir makalede, bir arka taraf güç dağıtım ağı uygulamasının, geleneksel ön taraf PDN’ye kıyasla açıklanmayan bir işlemci alanında %14,8’lik bir azalmaya neden olduğunu bildirdi. Bu arada, makale özellikle sırasıyla %10,6 ve %19’luk alan düşüşleri gözlemledikleri iki Kol devresini vurguladı. %10 ila %19 kalıp alanı azaltma, birinin %10 ila %19 daha fazla transistör paketlemesini ve performans kazanmasını veya belirli bir çipin maliyetlerini azaltmasını sağladığı için büyük bir avantaj.

Samsung’un makalesinde bahsettiği bir diğer şey de kablolama uzunluğunda %9,2’lik bir azalma. Arka taraf güç rayı tipik olarak daha düşük dirence sahip daha kalın tellere izin veriyor ve bu nedenle daha yüksek performans için daha yüksek akımları çalıştırabilir. Kablolama uzunluğunun daha da azaltılması, ek performans avantajları da getirebilir.

Samsung’un ortaya çıkardığı arka taraf güç dağıtımının kolaylaştırdığı ek avantajlar, %3,6 Fmax iyileştirmesi, standart blok alanında %2,4 azalma ve %1,6 standart blok performansı iyileştirmesi sağlayan tasarım teknolojisi co-optimizasyon düğmeleri.

Bu yılın başlarında Intel, 20A (2nm sınıfı) üretim teknolojisi ve sonrasında kullanılacak PowerVia arka taraf güç dağıtım ağını detaylandırdı. Arka taraf güç rayı kullanmanın faydaları yaygın olarak kabul ediliyor ve Samsung’un bulguları da teoriyi kanıtlıyor. Güç kabloları, güç raylarını arkaya kaydırarak ve G/Ç kablolarından izole ederek daha önemli hale getirilebilir. Bu kalınlaşma, son üretim aşamalarındaki dirençleri azaltarak performansı artırıyor ve enerji kullanımını azaltıyor. Ek olarak, bu ayrım, maliyet tasarrufu sağlayan azaltılmış bir mantık alanına yol açıyor.

Samsung, BS PDN’sini ne zaman ve hangi düğümle uygulamayı planladığını açıklamadı. Şirket şu anda 2. Nesil 3nm sınıfı kapı çok yönlü transistör tabanlı SF3 imalat teknolojisini parlatıyor ve 2024’te seri üretim için kullanmayı hedefliyor. Şirketin ayrıca 2025’te SF3P ve 2nm sınıfı SF2’si var. Samsung’un gelecek yıl SF3 için bir arka güç rayı kullanması pek olası olmasa da, şirket BS PDN’sini 2025’te SF3P veya SF2’de uygulamayı düşünebilir.